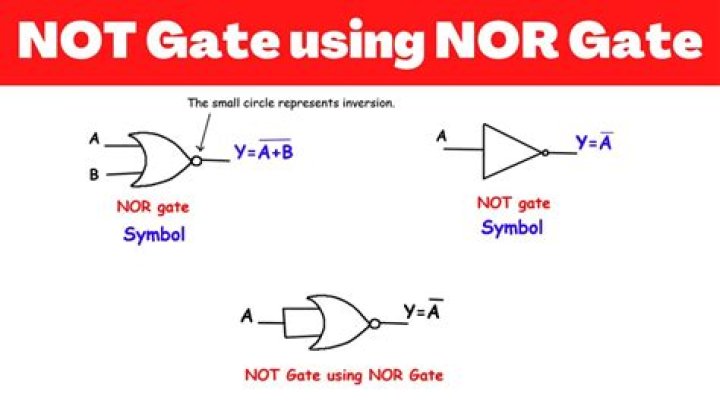

Primitive not gate with more than one input

Matthew Martinez

Matthew Martinez

I came found this example when reading a Verilog article, in which it discusses about a not gate with two inputs.

Is there anyone here who can explain what this means?

module buf_not_gates (input a, b, output c, d); buf (c, a, b); // c is the output, a and b are inputs not (d, a, b); // d is the output, a and b are inputs

endmodule

module buf_not_gates_tb; reg a, b; wire c, d; buf_not_gates Instance0 (a, b, c,d); initial begin a = 0; b = 0; #1 a = 0; b = 1; #1 a = 1; b = 0; #1 a = 1; b = 1; end initial begin $monitor ("T=%t| a=%b |b=%b| c(buf)=%b |d(not)=%b", $time, a, b, c, d); end

endmodule1 Answer

The comments in that code are incorrect. The not gate does not have 2 inputs; neither does buf. According to IEEE Std 1800-2017, section 28.5 buf and not gates:

These two logic gates shall have one input and one or more outputs. The last terminal in the terminal list shall connect to the input of the logic gate, and the other terminals shall connect to the outputs of the logic gate.

In this line of code:

buf (c, a, b);b is the only input to the buf instance; c and a are outputs.

It looks like the article author mistakenly copied the code from the bufif_notif_gates example.