Prefered syntax for verilog module declaration

Emily Wong

Emily Wong

I am relatively new to FPGAs, and I am looking for some guidance for modern best practice regarding the declaration of modules in Verilog.

I have seen two ways of declaring a module in verilog. The first reminds me of Traditional C, such as the examples on wikipedia:

module toplevel(clock,reset); input clock; input reset; /* snip */

endmoduleWhereas the alternative syntax has the input/output specifier as part of the argument list, not too dissimilar to VHDL, as in this example:

module fadder( input a, //data in a input b, //data in b input cin, //carry in output sum_out, //sum output output c_out //carry output

);

/* snip */

endmoduleFor newly written verilog code, which syntax is preferred? "Preferred", in this instance, means something written in a standard or related material (either explicitly written, or implicitly by examples given in the standard), or written in a well-regarded style guide. The question isn't asking for a personal preference!

3 Answers

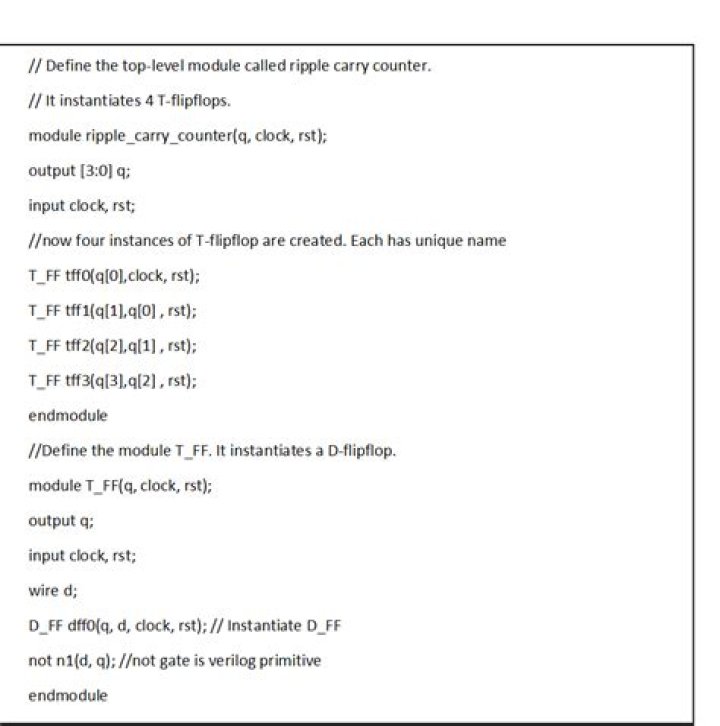

The second syntax form was indented to replace the first syntax form. If you look at the 1364-2001 Verlog LRM, as well as the current 1800-2012 SystemVerilog LRM, you will notice that all examples of module declarations use the second form. The first form is only there for legacy, but unfortunately, it has taken longer than expected for textbooks and course material to switch over.

The key benefit of this newer (or ANSI-style) syntax is that you only have to declare your port name in one place. With the older syntax, you had to declare a port name up to three times; once for the positional ordering, another time for the port direction, and if the port needed to be something other than a wire, a third time to declare its data type.

0The second is preferred. This was introduced in Verilog 2001. This is often called "ANSI-style".

When I teach Verilog I teach both, but recommend ANSI-style for all new code. (And mention that I am only teaching the first style so that the students can understand legacy code.)

If you get on to System-Verilog, you will find that some things only work with ANSI-style anyway.

6The second mode is preferred but there is a case where you might want to use the first one. This is if you have lots of complex calculations to be done on parameters to get to the right port widths. Below is just a small artificial example. Yes, you can replace the localparam with their expressions but that may make your code unreadable.

I think it is one of the omission of (system) Verilog that you can't use local_param after a #(parameter.. definition.

module example

#(parameter L2DEPTH = 8, OFFSET = 2

)

(siga,sigb,sigc,sig_out);

localparam DEPTH = 1<<L2DEPTH;

localparan TOP = DEPTH+OFFSET;

localparam BOT = DEPTH-OFFSET;

localparam DBLDEPTH = 2<<L2DEPTH;;

input [ L2DEPT-1:0] siga;

input [ TOP-1:0] sigb;

input [ BOT-1:0] sigc;

output [DBLDEPTH-1:0] sig_out;