in VHDL, is it possible to create an array of std_logic_vector without using a type?

Matthew Harrington

Matthew Harrington

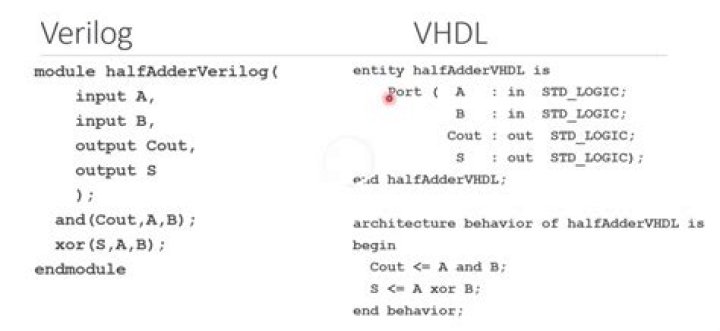

In SystemVerilog I can create a multidimensional array as follows:

reg [31:0] mem[0:127];However, in VHDL all of the examples for create a similar multidimensional arrays online in the VHDL book show that I must first create a type before creating the array. Example:

type mem_t is array(0 to 127) of std_logic_vector(31 downto 0);

signal mem :mem_t;Is it possible to do this all in one step in VHDL like in verilog without first creating a type for the array? Example:

signal mem :array(0 to 127) of std_logic_vector(31 downto 0);

--syntax error:GHDL: Type mark expected in a subtype indication

--syntax error:vsim: near "array": (vcom-1576) expecting STRING or IDENTIFIER or << or '('The reason why i'm asking is because i'm trying to avoid the use of a package to declare an array type, when connecting IO with an array that is connected between to modules in VHDL.

12 Answers

What you created is an array of an array - which is in general what you want. What @Matthew Taylor created is a multidimensional array.

WIth VHDL-2008 the elements of a composite can be unconstrained, and hence, you can create:

type std_logic_aoa is array (natural range <>) of std_logic_vector;Realistic speaking this should be in a standard library - it is just not there currently.

And then you can use it by doing:

signal mem : std_logic_aoa (0 to 127)( 31 downto 0);The reason you want an array of an array here is it allows you to do things like:

signal Data : std_logic_vector(31 downto 0) ;

. . .

Data <= mem(15) ; No. It isn't.

It is possible to create genuinely multi-dimensional arrays in VHDL, but you still need to create a new type. That is the VHDL way. So, you'll still need your package.

Here's a multi-dimensional constrained array:

type c_mem_t is array (0 to 127, 31 downto 0) of std_logic;and here's a multi-dimensional unconstrained array:

type mem_t is array (natural range <>, natural range <>) of std_logic;And you use them like this:

signal mem : c_mem_t;

signal mem : mem_t(0 to 127, 31 downto 0);In VHDL-2002 either both dimensions must be constrained or both must be unconstrained. In VHDL-2008, you can have one constrained and one not:

type mem_t_2008 is array (natural range <>, 31 downto 0) of std_logic;